### Specification

for

### micro QUAD SMALL FORM-FACTOR PLUGGABLE FOUR CHANNEL PLUGGABLE TRANSCEIVER, HOST CONNECTOR, & CAGE ASSEMBLY FORM FACTOR

Rev 2.5 September 11, 2017

Abstract: The micro QUAD SMALL FORM-FACTOR PLUGGABLE (microQSFP) specification defines requirements for a form factor supporting up to four electrical channels, high system density, and a high performance thermal solution. Support for 28 Gb/s signal rates on each channel enables many applications including 10 Gigabit Ethernet, 25 Gigabit Ethernet, 50 Gigabit Ethernet, 100 Gigabit Ethernet, 16GFC, 32GFC, and 128GFC, where higher densities are required than are possible with existing form factors. Included are definitions of electrical, mechanical, and management interfaces, electrical connector, guide rail (cage), front panel and host PCB layout, and optical connector options. By addressing the thermal, signal integrity, electromagnetic, and electrostatic challenges of a high density solution, the microQSFP Specification enables higher density networking solutions that are critical to support the continuing network demand.

This document provides a common specification for systems manufacturers, system integrators, and suppliers of modules.

POINTS OF CONTACT:

Nathan Tracy Chairman TE Connectivity 3101 Fulling Mill Road Middletown, PA 17057 Ph: 717-986-7546 ntracy at te dot com Joshua Sechrist Technical Editor Intel Corporation 2501 NE Century Boulevard Hillsboro, OR 97124 Ph: 503-613-7103 Joshua dot Sechrist at intel dot com

Limitation on use of Information:

This specification is provided "as is" with no warranties whatsoever, including any warranty of merchantability, non-infringement, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification or sample. The microQSFP promoters disclaim all liability, including liability for infringement of any proprietary rights, relating to use of information in this specification. In no event shall the microQSFP promoters, contributors or adopters be liable for any direct, indirect, special, exemplary, punitive, or consequential damages, including, without limitation, lost profits, even if advised of the possibility of such damages.

This specification may contain, and sometimes even require the use of intellectual property owned by others. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein, except that a license is hereby granted to copy and reproduce this specification for internal use only.

Permissions:

You are authorized to download, reproduce and distribute this document. All other rights are reserved. The provision of this document should not be construed as the granting of any right to practice, make, use or otherwise develop products that are based on the document. Any and all IP rights related to this document and the designs disclosed within, except for the rights expressly mentioned above, are reserved by the respective owners of those IP rights.

Page 1

### EXPRESSION OF SUPPORT BY MANUFACTURERS

As of the publication date, the following are promoter member companies of the microQSFP MSA.

Broadcom Brocade Cisco Dell Foxconn Interconnect Technology Huawei Intel Lumentum Juniper Networks Microsoft Molex TE Connectivity

As of the publication date, the following are contributor member companies of the microQSFP MSA.

Amphenol Applied Optoelectronics Inc Finisar Lorom Luxshare ICT MACOM MultiLane SAL Oclaro, Inc. Rosenberger Semtech Change History:

| Revision |                  | Changes                                                                                                                          |

|----------|------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | January 14, 2016 | -First Public Release, released as Draft Mechanical Only Specification.                                                          |

| 2.0      | March 17, 2016   | -Second Public Release, released as Complete MSA Specification                                                                   |

|          |                  | -Various editorial changes to text, figures, and tables.                                                                         |

|          |                  | -Contributor members added, Amphenol, Finisar, Lorom,<br>MulitLane SAL, Oclaro, Inc, Rosenberger, and Semtec.                    |

|          |                  | -Table of contents updated.                                                                                                      |

|          |                  | -Content of Clause 4 content moved to Subclause 4.1.                                                                             |

|          |                  | -Content added in Subclause 4.1, including text prior to figure 1, and table 1, figure 2a, figure 2b and content after figure 1. |

|          |                  | -Contact 31 changed from TBA* to VccMgmt in figure 1.<br>Contact defined in detail in Subclauses in Clause 4.                    |

|          |                  | -Subclauses 4.2, 4.3, 4.4, 4.5, and 4.6 created. Includes all text, items, table 2, table 3, & Figure 3                          |

|          |                  | -Table 2 is now Table 4. Listed figures in table 4 updated to reference new figure numbers.                                      |

|          |                  | -Figures 3, 4, 5, 6, 7, 8, 9, 10, 11, & 12, are now figures 5, 6, 7, 8, 9, 10, 11, 12, 13, & 14 respectively.                    |

|          |                  | -RFS Symbol removed from all feature control frames found in the figures 6, 7, 8, 9, 12, $\&$ 13.                                |

|          |                  | -Contact numbers identified in figures 6, 7, 9, & 12.                                                                            |

|          |                  | -In figure 8, 2X 40.84 BASIC added, Keepout zones identified.                                                                    |

|          |                  | -In figure 9, LMC changed to MMC on feature control frame associated with 1.05 hole identifying datum J.                         |

|          |                  | -In figure 12, rear of connector enlarged, dim 11.75 from datum L was 9.95, and dim 6.75                                         |

|          |                  | -Content from clause 6 moved to Subclause 6.2, and content of Subclause 6.1 created including table 6.                           |

|          |                  | -Clause 7 (Management Interface) content created.                                                                                |

| microOSFP  | Specification | Rev   | 2.5 |

|------------|---------------|-------|-----|

| THE TOYOTT | opcorrigation | ICC V | 2.0 |

|     |                  | microQSFP Specification Rev 2.5                                                                                                                                                                     |  |  |  |  |

|-----|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 2.1 | May 26, 2016     | -Various editorial changes to text, figures, and tables.                                                                                                                                            |  |  |  |  |

|     |                  | -Contributor member added, MACOM.                                                                                                                                                                   |  |  |  |  |

|     |                  | -Table of contents updated.                                                                                                                                                                         |  |  |  |  |

|     |                  | -Subclause 4.3.2 updated with reference to Subclause 7.3.10.                                                                                                                                        |  |  |  |  |

|     |                  | -Extended Identifier Table 8 created, placed in Subclause 7.2.1. Table numbers re-ordered after Table 8. Subclauses 7.2.2 and 7.2.3 continue after inserted Subclause 7.2.1.                        |  |  |  |  |

|     |                  | -DataPathInit duration clarified in Subclause 7.3.3.                                                                                                                                                |  |  |  |  |

|     |                  | -TX_TurnOn duration clarified in Subclause 7.3.5.                                                                                                                                                   |  |  |  |  |

|     |                  | -2 Second Timeout Removed from Figures 15 & 16, all timing placed in new Table 12 in Subclause 7.3.10                                                                                               |  |  |  |  |

| 2.2 | June 03, 2016    | -Third public release.                                                                                                                                                                              |  |  |  |  |

|     |                  | -Various editorial changes.                                                                                                                                                                         |  |  |  |  |

|     |                  | -Replaced Page 03h Byte 252 with Lower Memory Byte 114 in all instances.                                                                                                                            |  |  |  |  |

| 2.3 | September 09,    | -Fourth public release.                                                                                                                                                                             |  |  |  |  |

|     | 2016             | -Figure 6 dimension changes as follows: 44.1 MAX internal depth of note 6 was 44 MAX, 9.2 distance from latch to cage stop was 9.1, 15.9 MAX distance from cage stop to front of module was 16 MAX. |  |  |  |  |

|     |                  | -Figure 7 dimension changes as follows: (2.6) contact point distance was (2.5), 3.1 distance front edge of module card to edge of pad was 3.                                                        |  |  |  |  |

| 2.4 | January 13, 2017 | -0111b in Table 10 now assigned to 1 to 5 seconds, all subsequent times shift down 1 row in table 10.                                                                                               |  |  |  |  |

|     |                  | -Clause 8, Appendix A was created. Appendix A covers interface definitions for modules and connectors that support PCIe applications.                                                               |  |  |  |  |

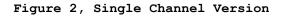

| 2.5 | August 28, 2017  | -Figures 2 & 3 and supporting detail added in Subclause 4.1, for single and two channel modules positions.                                                                                          |  |  |  |  |

|     |                  | -Figures re-numbered starting with figure 4.                                                                                                                                                        |  |  |  |  |

|     |                  | -Clause 9.0 Appendix B for 1, 2, & 4 Channels added.                                                                                                                                                |  |  |  |  |

| 1. Scope                                                                      | 6           |

|-------------------------------------------------------------------------------|-------------|

| 1.1 Description of Clauses                                                    | 6           |

| 2. References                                                                 | 6           |

| 2.1 Industry Documents                                                        | 6           |

| 2.2 SFF Specifications                                                        | 7           |

| 2.3 Sources                                                                   | 7           |

| 2.4 Conventions                                                               | 7           |

| 3. Introduction                                                               | 7           |

| 4. Electrical Specification                                                   | 7           |

| 4.1 Electrical Interface                                                      | 8           |

| 4.2 Low Speed Signal Descriptions                                             | 12          |

| 4.2.1 ModSelL                                                                 | 12          |

| 4.2.2 ResetL                                                                  | 12          |

| 4.2.3 ModPrsL                                                                 | 12          |

| 4.2.4 IntL                                                                    | 12          |

| 4.3 Low Speed Signal Electrical Specifications                                | 13          |

| 4.3.1 Low Speed Signaling                                                     | 13          |

| 4.3.2 Low Speed Signal Timing                                                 | 13          |

| 4.4 High Speed Signal Electrical Specifications                               | 13          |

| 4.4.1 Compliance Testing                                                      | 13          |

| 4.5 Power Requirements                                                        | 14          |

| 4.5.1 Power Classes and Maximum Power Consumption                             | 14          |

| 4.5.2 Module Power Supply Specification                                       | 14          |

| 4.5.3 Host Board Power Supply Noise Output                                    | 15          |

| 4.5.4 Module Power Supply Noise Output                                        | 15          |

| 4.5.5 Module Power Supply Noise Tolerance                                     | 15          |

| 4.6 ESD                                                                       | 15          |

| 5. Mechanical and Board Definition                                            | 15          |

| 5.1 Introduction                                                              | 15          |

| 5.2 microQSFP Reference Datums and Component Alignment                        | 16          |

| 5.3 microQSFP Module Mechanical Package Dimensions                            | 18          |

| 5.3.1 Mating of microQSFP Module PCB to microQSFP Electrical Connector        | 19          |

| 5.4 Host PCB Layout                                                           | 20          |

| 5.4.1 Insertion, Extraction and Retention Forces for microQSFP Modules        | 22          |

| 5.5 Color Coding and Labeling of microQSFP Modules                            | 22          |

| 5.6 Bezel for Systems using microQSFP Modules                                 | 23          |

| 5.6.1 Bezel for the Thru Bezel Cage Assembly                                  | 23          |

| 5.7 microQSFP Electrical Connector Mechanical                                 | 24          |

| 5.8 Individual microQSFP Cage Assembly                                        | 25          |

| 5.9 EMI Cover                                                                 | 26          |

| 5.10 Optical Interface                                                        | 26          |

| 6. Thermal                                                                    | 28          |

| 6.1 Thermal Requirements                                                      | 28          |

| 6.2 Thermal Management Considerations                                         | 28          |

| 7. Management Interface                                                       | 29          |

| 7.1 Introduction                                                              | 29          |

| 7.2 microQSFP Memory Map                                                      | 29          |

| 7.2.1 Extended Identifier                                                     | 30          |

| 7.2.2 Module_State Register Encodings                                         | 30          |

| 7.2.3 Transient State Duration Encodings                                      | 31          |

| 7.3 microQSFP State Machine                                                   | 31          |

| 7.3.1 MgmtInit State (Transient)                                              | 34          |

| 7.3.2 Configure State (Parked)                                                | 34          |

| 7.3.3 DataPathInit State (Transient)                                          | 35          |

| 7.3.4 TX_Off State (Parked)                                                   | 35          |

| 7.3.5 TX_TurnOn State (Transient)                                             | 35          |

| 7.3.6 MissionMode State (Parked)                                              | 36          |

| 7.3.7 RevertLowPower State (Transient)                                        | 36          |

| 7.3.8 Reset State (Parked)                                                    | 37<br>37    |

| 7.3.9 Interrupt Flag Applicability Per State                                  |             |

| microQSFP FOUR CHANNEL PLUGGABLE TRANSCEIVER, HOST CONNECTOR, & CAGE ASSEMBLY | FORM FACTOR |

|   | microQSFP                                                 | Specification | Rev 2.5 |

|---|-----------------------------------------------------------|---------------|---------|

|   | 7.3.10 Timing Requirements                                |               | 37      |

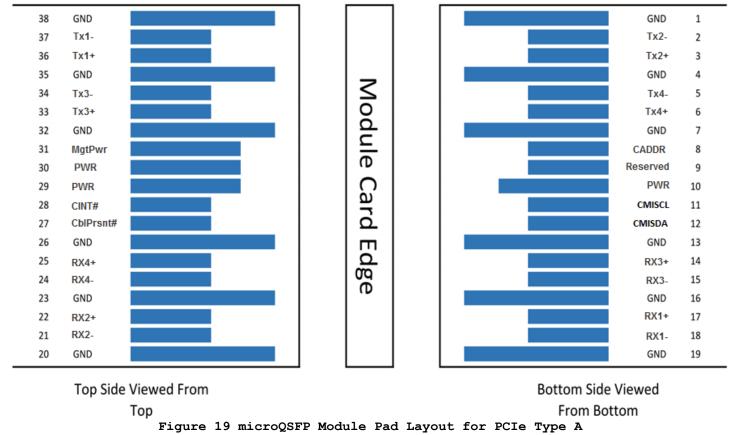

| 8 | . Appendix A                                              |               | 38      |

|   | 8.1 Introduction                                          |               | 38      |

|   | 8.2 Type A Electrical Specification for PCIe Applications |               | 38      |

|   | 8.2.1 Type A Electrical Interface for PCIe applications   |               | 38      |

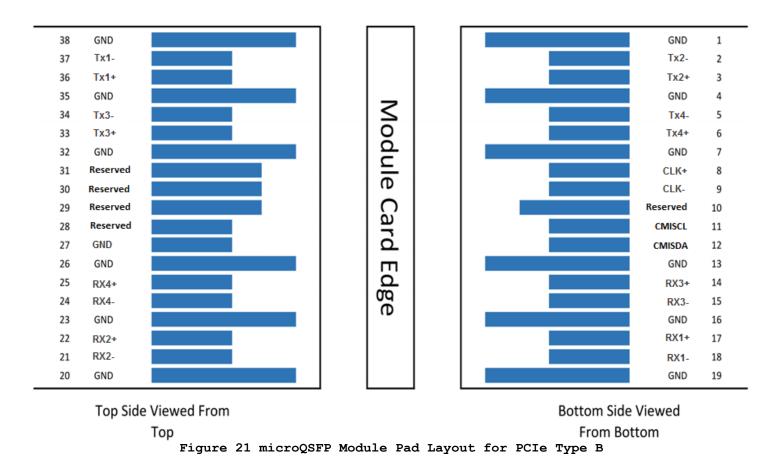

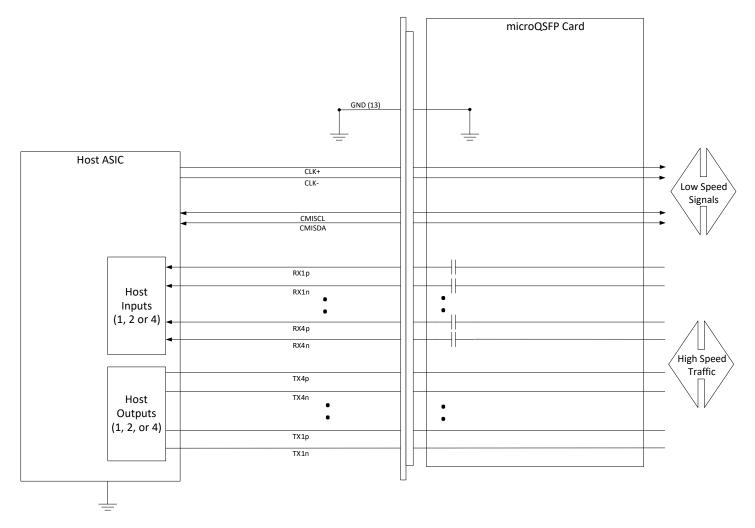

|   | 8.3 Type B Electrical Interface for PCIe Applications     |               | 42      |

| 9 | . Appendix B                                              |               | 45      |

|   | 9.1 1, 2, and 4 Channels Examples                         |               | 45      |

#### Scope 1.

This specification defines the electrical, management, and optical interfaces, the mechanical form factor, thermal requirements, EMI, and ESD requirements for a 1, 2, or 4channel (such as 28 GBd per channel) transmit/receive hot-pluggable module, connector, and cage. Clause 3 defines these items in more detail.

### 1.1 Description of Clauses

Clause 1 contains the Scope and Purpose

Clause 2 contains Referenced and Related Standards and Specifications

Clause 3 begins the specification

Clause 4 contains electrical specifications

Clause 5 contains mechanical specifications and printed circuit board recommendations

Clause 6 contains thermal considerations

Clause 7 is a description of the management interface and management register contents.

Clause 8 is Annex A defining signal symbols and contact numbering for PCIe applications

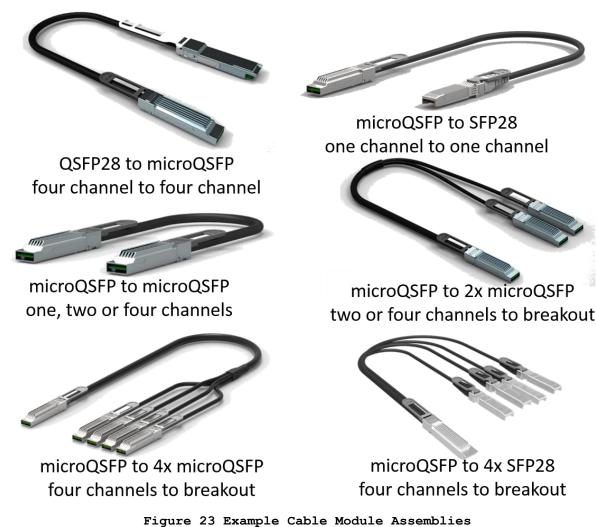

Clause 9 is Annex B showing examples of 1, 2, 4 channel and breakout applications

### 2. References

\_ \_

\_

The microQSFP MSA activities support the requirements of the networking, computing, and storage industries.

### 2.1 Industry Documents

The following interface standards and specifications are relevant to this Specification.

| GR-253-CORE                                                                    |

|--------------------------------------------------------------------------------|

| IEEE Std 802.3-2015                                                            |

| IEEE Std 802.3by 25 Gb/s Ethernet, amendment to 802.3-2015                     |

| IEEE Std 802.3cd 50Gb/s, 100Gb/s, 200Gb/s Ethernet, Draft amendment 802.3-2015 |

| InfiniBand Architecture Specifications FDR, EDR and draft HDR                  |

| FC-PI-5, FC-PI-6, FC-PI-6P                                                     |

| FC-PI-7 64GFC/256GFC Project                                                   |

| SAS 4.0                                                                        |

| Optical Connectors: MPO: IEC 61754-7, Dual LC: IEC 61754-20                    |

| Aligned key (Type B) MPO patch cords: TIA-568                                  |

| Dual LC optical patch cord: NEBS GR-63                                         |

| SFF-8665 QSFP+ 28 Gb/s 4X Pluggable Transceiver Solution (QSFP28)              |

| SFF-8636 Management Interface for Cabled Environment (Revision 2.9)            |

| SFF-8679 OSFP28 4X Base Electrical Specification (Revision 1.7)                |

- PCI Express External Cabling Spec (Revision 3.0, Version 0.7)

- 25G 50G Ethernet Consortium, Schedule 3 Specification, Rev. 1.6

Page 6

### 2.2 SFF Specifications

A possible action of the MSA is to create appropriate SFF specifications based on this MSA.

### 2.3 Sources

This document can be obtained via the www.microqsfp.com web site

### 2.4 Conventions

The ISO convention of numbering is used i.e., the thousands and higher multiples are separated by a space and a period is used as the decimal point. This is equivalent to the English/American convention of a comma and a period.

| English     |   | French |       |   | ISO |       |  |  |

|-------------|---|--------|-------|---|-----|-------|--|--|

| 0.6         |   |        | 0,6   |   |     | 0.6   |  |  |

| 1,000       |   | 1      | 000   |   | 1   | 000   |  |  |

| 1,323,462.9 | 1 | 323    | 462,9 | 1 | 323 | 462.9 |  |  |

### 3. Introduction

This Specification covers the following items:

a) Electrical interfaces (including contact assignments for data, control, status, configuration and test signals) and the electrical Connector and recommended host PCB layout.

b) Management interfaces encompassing features from the current QSFP28 SFF documents and includes support for multiple physical media (copper, optics etc), specific multi-data rate and multi-protocol implementations.

c) Optical interfaces including the optical Connector receptacle and mating fiber optic Connector plug and recommended breakout cable assembly. The optical specifications are left to the applicable standards for each protocol.

d) Mechanical definitions including package outline with latching detail and optical Connector receptacle detail, electrical Connector mechanical details for both the Module and host PCB halves, front panel cut-out recommended dimensions.

e) Thermal requirements and considerations.

f) Electromagnetic interference (EMI) recommendations, including necessary shielding features to seal the OEM chassis front panel output with and without the microQSFP Module installed in the Cage.

g) Electrostatic discharge (ESD) requirements solely to the extent disclosed in the Specification where the sole purpose of such disclosure is to enable products to operate, connect or communicate as defined within the Specifications.

The Specifications will provide a common solution for combined four-channel ports that support OTN and/or Ethernet and/or InfiniBand and/or Fibre Channel specifications. This specification encompasses design(s) capable of supporting multimode, single-mode Modules, passive copper, active copper, and active optical cables. Electrical and optical specifications may be compatible with standards under development.

### 4. Electrical Specification

This microQSFP Specification adopts the compliance electrical and timing requirements found in Clauses 4, 5, and 8 of SFF-8679 except as noted here in Clause 4. The scope of SFF-8679 includes: electrical contacts for the host Connector, fiber positions for optical interfaces, power supply requirements, ESD, and thermal characteristics of pluggable modules and direct attach cables. Any exceptions to SFF-8679 will be defined in this specification.

microQSFP FOUR CHANNEL PLUGGABLE TRANSCEIVER, HOST CONNECTOR, & CAGE ASSEMBLY FORM FACTOR

### 4.1 Electrical Interface

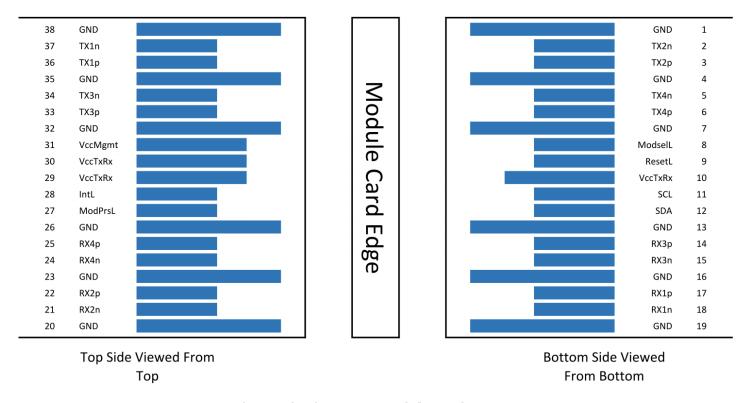

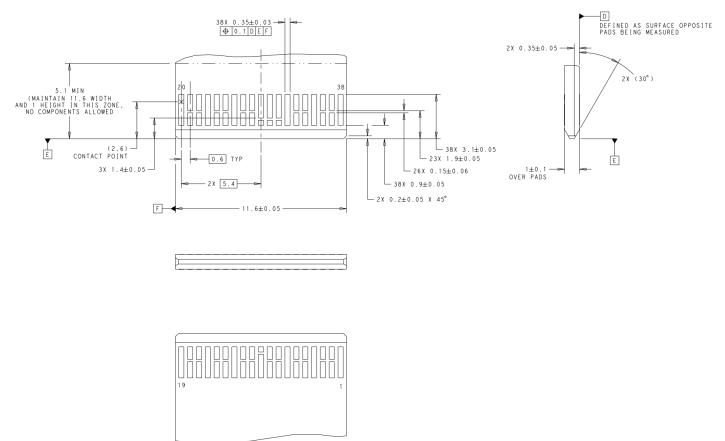

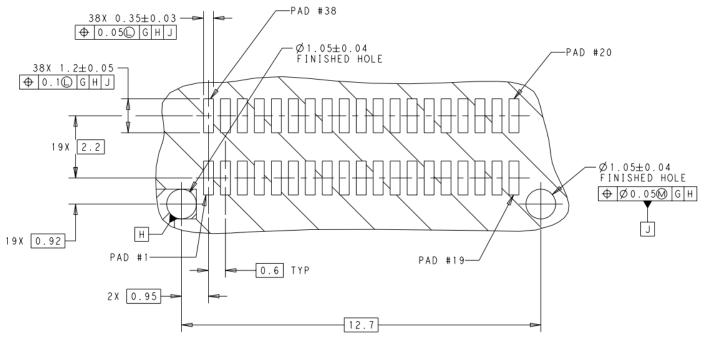

Electrical Interface and connector definitions of SFF-8679 Rev 1.7 Subclause 5.1 are replaced by this Subclause 4.1. Figure 1 shows the signal symbols and contact numbering for the microQSFP Module edge Connector. The diagram shows the Module PCB edge as a top and bottom view. There are 38 contacts intended for high speed signals, low speed signals, power, and ground connections. Table 1 contains the microQSFP Module Electrical Interface Map.

The module contains a printed circuit board that mates with the electrical connector. The pads are designed for a sequenced mating:

```

First mate - ground contacts

Second mate - power contacts

Third mate - signal contacts

```

For EMI protection the signals to the connector should be shut off when the module is removed. Standard board layout practices such as connections to Vcc and GND with Vias, use of short and equal-length differential signal lines, use of microstrip-lines and 50 Ohm terminations are recommended. The chassis ground (case common) of the module should be isolated from the module's circuit ground, GND, to provide the equipment designer flexibility regarding connections between external electromagnetic interference shields and circuit ground, GND, of the module.

Figure 1 microQSFP Module Pad Layout

### microQSFP Specification Rev 2.5 Table 1: microQSFP Module Electrical Interface Map

| # Logic Symbol |                | Symbol  | Name                                            | Plug     | Notes |  |

|----------------|----------------|---------|-------------------------------------------------|----------|-------|--|

|                |                | Sympot  | Nalle                                           | Sequence | NOLES |  |

| 1              |                | GND     | Signal Ground                                   | 1        | 1     |  |

| 2              | CML-I          | Tx2n    | Transmitter Inverted Data Input                 | 3        |       |  |

| 3              | CML-I          | Tx2p    | Transmitter Non-Inverted Data Input             | 3        |       |  |

| 4              |                | GND     | Signal Ground                                   | 1        | 1     |  |

| 5              | CML-I          | Tx4n    | Transmitter Inverted Data Input                 | 3        |       |  |

| 6              | CML-I          | Tx4p    | Transmitter Non-Inverted Data Input             | 3        |       |  |

| 7              |                | GND     | Signal Ground                                   | 1        | 1     |  |

| 8              | LVTTL-I        | ModSelL | Module Select                                   | 3        |       |  |

| 9              | LVTTL-I        | ResetL  | Module Reset                                    | 3        |       |  |

| 10             |                | VccTxRx | +3.3V Power Supply for high-speed data path ICs | 2        | 2     |  |

| 11             | LVCMOS-<br>I/O | SCL     | 2-wire serial interface clock                   | 3        |       |  |

| 12             | LVCMOS-<br>I/O | SDA     | 2-wire serial interface data                    | 3        |       |  |

| 13             |                | GND     | Signal Ground                                   | 1        | 1     |  |

| 14             | CML-O          | Rx3p    | Receiver Non-Inverted Data Output               | 3        |       |  |

| 15             | CML-O          | Rx3n    | Receiver Inverted Data Output                   | 3        |       |  |

| 16             |                | GND     | Signal Ground                                   | 1        | 1     |  |

| 17             | CML-O          | Rx1p    | Receiver Non-Inverted Data Output               | 3        |       |  |

| 18             | CML-O          | Rx1n    | Receiver Inverted Data Output                   | 3        |       |  |

| 19             |                | GND     | Signal Ground                                   | 1        | 1     |  |

| 20             |                | GND     | Signal Ground                                   | 1        | 1     |  |

| 21             | CML-O          | Rx2n    | Receiver Inverted Data Output                   | 3        |       |  |

| 22             | CML-O          | Rx2p    | Receiver Non-Inverted Data Output               | 3        |       |  |

| 23             |                | GND     | Signal Ground                                   | 1        | 1     |  |

| 24             | CML-O          | Rx4n    | Receiver Inverted Data Output                   | 3        |       |  |

| 25             | CML-O          | Rx4p    | Receiver Non-Inverted Data Output               | 3        |       |  |

| 26             |                | GND     | Signal Ground                                   | 1        | 1     |  |

| 27             | LVTTL-O        | ModPrsL | Module Present                                  | 3        |       |  |

| 28             | LVTTL-O        | IntL    | Interrupt                                       | 3        |       |  |

| 29             |                | VccTxRx | +3.3V Power Supply for high-speed data path ICs | 2        | 2     |  |

| 30             |                | VccTxRx | +3.3V Power Supply for high-speed data path ICs | 2        | 2     |  |

| 31             |                | VccMgmt | Management Interface Power Supply               | 2        | 2     |  |

| 32             |                | GND     | Signal Ground                                   | 1        | 1     |  |

| 33             | CML-I          | Тх3р    | Transmitter Non-Inverted Data Input             | 3        |       |  |

| 34             | CML-I          | Tx3n    | Transmitter Inverted Data Input                 | 3        |       |  |

| 35             |                | GND     | Signal Ground                                   | 1        | 1     |  |

| 36             | CML-I          | Tx1p    | Transmitter Non-Inverted Data Input             | 3        |       |  |

| 37             | CML-I          | Tx1n    | Transmitter Inverted Data Input                 | 3        | 1     |  |

|                |                | GND     | Signal Ground                                   | 1        | 1     |  |

Note 1: GND is the symbol for signal and supply (power) common for the microQSFP Module All are common within the microQSFP Module and all Module voltages are referenced to this potential unless otherwise noted. Connect these directly to the host board signalcommon ground plane.

Note 2: Each Vcc contact is limited to maximum of 1 A. The Host shall apply power to all Vcc contacts (VccTxRx and VccMgmt) concurrently. All VccTxRx contacts may lead to a common 3.3 V Power Supply in the module. This 3.3 V Power Supply shall be electrically isolated from the VccMgmt Power Supply in the module.

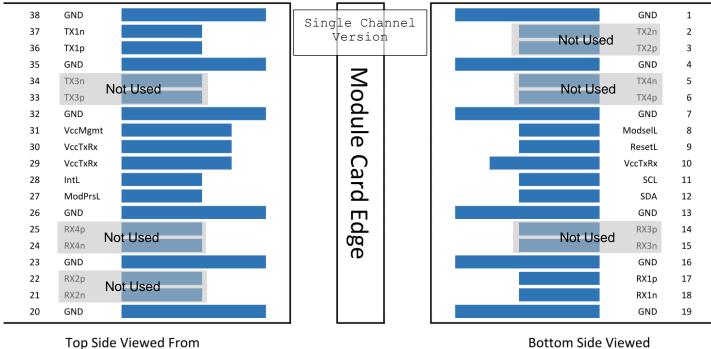

### 4.1.1 Configurations

microQSFP has 4 electrical channels, but can support implementations with either 1, 2, or 4 electrical channels. In the 1 and 2 channel implementations, the specific electrical channels that must be used are shown in Figures 2 and 3. The un-used high speed gold mating pads on the module/cable plug card edge must still be included on the printed circuit board even in these reduced channel versions to protect the durability of the host receptacle connector contacts. In one and two channel module

microQSFP FOUR CHANNEL PLUGGABLE TRANSCEIVER, HOST CONNECTOR, & CAGE ASSEMBLY FORM FACTOR

implementations, the un-used gold mating pads on the module/cable plug can be left "open circuit". In all cases the microQSFP host receptacle connector is required to include all 38 contacts as shown in Figure 1. Annex B shows some example use cases for 1, 2, and 4 channel implementations used in point to point and breakout applications as well as defining the necessary memory map details for these cases.

Тор

microQSFP Specification Rev 2.5

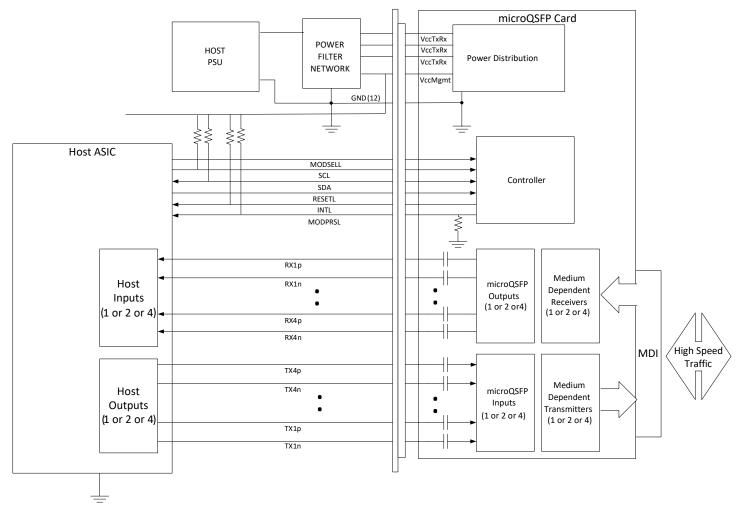

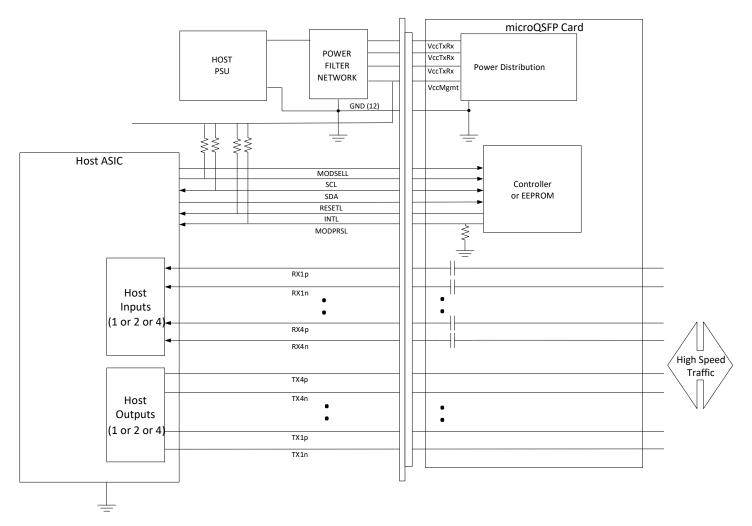

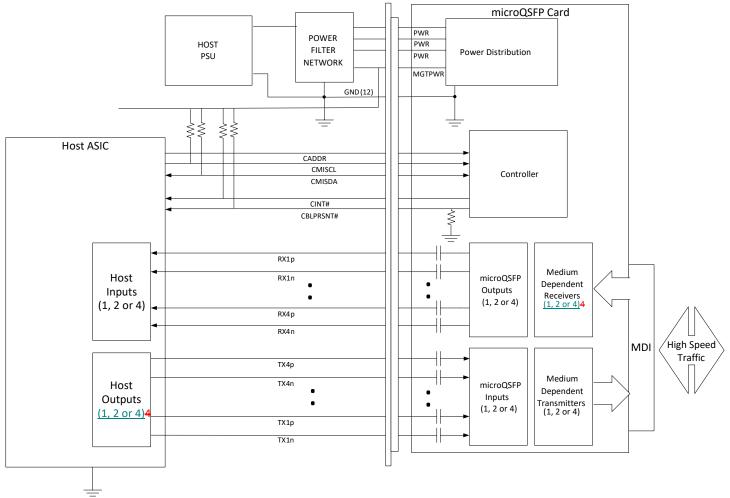

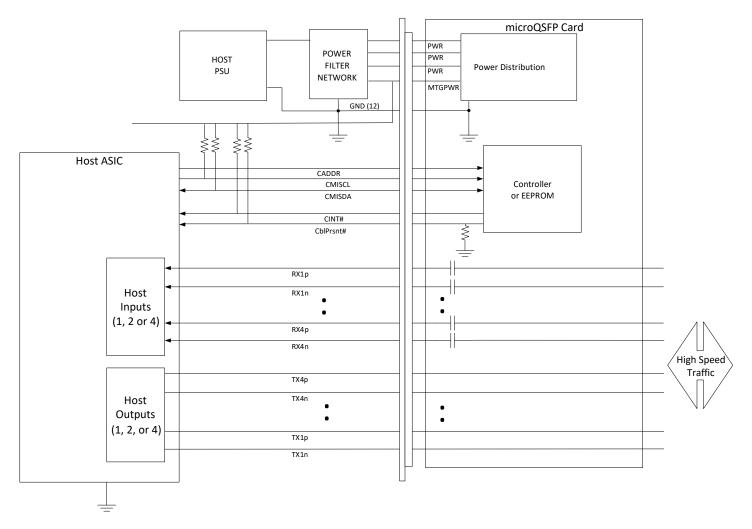

Figure 4 shows an example block diagram of the connectivity between the host PCB and the microQSFP module.

microQSFP FOUR CHANNEL PLUGGABLE TRANSCEIVER, HOST CONNECTOR, & CAGE ASSEMBLY FORM FACTOR

Page 10

Figure 4a: Example microQSFP Host Board and Optical Module Block Diagram

### Figure 4b Example microQSFP Host Board and Copper Cable Module Block Diagram

### 4.2 Low Speed Signal Descriptions

Low Speed Signals are as defined in Subclause 5.2 of SFF-8679 except as follows. The signal, LPMode, has been deleted. In addition to the 2-wire serial interface the module has the following low speed pins for control and status:

ModSelL ResetL ModPrsL IntL

### 4.2.1 ModSelL

For ModSelL see Subclause 5.2.1 in SFF-8679.

### 4.2.2 ResetL

For ResetL see Subclause 5.2.2 in SFF-8679.

### 4.2.3 ModPrsL

For ModPrsL see Subclause 5.2.4 in SFF-8679 except that in the module, ModPrsL is connected to module Signal Ground through no more than 150 Ohm.

### 4.2.4 IntL

IntL is as described in SFF-8679 Subclause 5.2.5

### 4.3 Low Speed Signal Electrical Specifications

Low speed signal electrical specifications are as defined in SFF-8679 except Subclause 4.3.1 below replaces Subclause 5.3.1 of SFF-8679.

### 4.3.1 Low Speed Signaling

Low speed signaling shall utilize the VccMgmt rail for all pull-ups or actively driven high signals. Hosts shall use a pull-up resistor connected to VccMgmt on each of the 2wire interface SCL (clock), SDA (data), and all low speed status outputs. Module pullups on SCL and SDA signals are not required. If the Module implementation uses pullups on these signals, each pullup shall be at least 47k Ohms.

The SCL and SDA comprise a hot plug interface that may support a bus topology. During module insertion or removal, the module may implement a pre-charge circuit which prevents corrupting data transfers from other modules that are already using the bus.

When active modules are in low power mode, the module receiver high speed signal outputs shall be quiescent and the transmitter optical outputs shall be disabled.

Compliance with Table 2 provides compatibility between host bus masters and the 2-wire interface.

| Parameter                                      | Symbol | Min         | Max Un        |    | Condition                                              |

|------------------------------------------------|--------|-------------|---------------|----|--------------------------------------------------------|

| SCL and SDA                                    | VOL    | 0           | 0.4           | V  | <pre>IOL(max)=3.0mA</pre>                              |

|                                                | VOH    | VccMgmt-0.5 | VccMgmt+0.3   | V  |                                                        |

| SCL and SDA                                    | VIL    | -0.3        | VccMgmt*0.3   | V  |                                                        |

|                                                | VIH    | VccMgmt*0.7 | VccMgmt + 0.5 | V  |                                                        |

| Capacitance for<br>SCL and SDA I/O<br>contacts | Ci     |             | 14            | pF |                                                        |

| Total bus<br>capacitive load                   | Cb     |             | 100           | pF | 3.0 k Ohms pullup resistor, max                        |

| for SCL and SDA                                |        |             | 200           | pF | 1.6 k Ohms pullup<br>resistor max                      |

| Reset and<br>ModSelL                           | VIL    | -0.3        | 0.8           | V  | Iin <=125 uA for<br>OV <vin, td="" vccmgmt<=""></vin,> |

|                                                | VIH    | 2           | VccMgmt+0.3   | V  |                                                        |

| ModPrsL and                                    | VOL    | 0           | 0.4           | V  | IOL=2.0mA                                              |

| IntL                                           | VOH    | VccMgmt-0.5 | VccMgmt+0.3   | V  |                                                        |

### Table 2: Low Speed Signals Electrical Specification

### 4.3.2 Low Speed Signal Timing

For exceptions and additions to Subclause 8.1 of SFF-8679, see Table 12 in Subclause 7.3.10.

All other Low Speed Signal Timing requirements are defined in SFF-8679 Subclause 5.3.2.

### 4.4 High Speed Signal Electrical Specifications

High Speed Signal Electrical Specifications are defined in SFF-8679 Subclause 5.4.

### 4.4.1 Compliance Testing

microQSFP Specification Rev 2.5 Compliance Testing requirements are as defined in SFF-8679 Clause 4 with the following exception. In Table 4-1, add to the description of TP1A, "Used to calibrate module test inputs at TP1."

### 4.5 Power Requirements

The following is in replacement of Subclause 5.5 in SFF-8679.

The electrical connector has three contacts labeled VccTxRx and one contact labeled VccMgmt. Each contact can concurrently support up to 1 Ampere current. The three VccTxRx contacts are in parallel and may connect to a common 3.3 V Power Supply in the module associated with the high speed signal path. The VccMgmt contact connects to a 3.3 V VccMgmt supply associated with the low speed (control) signal interface and memory. The VccTxRx supply is electrically isolated in the module from the VccMgmt supply.

The host system controls whether the module is in the low-power or high-power state via the management interface. Details of the initialization sequence are provided in Clause 7.

### 4.5.1 Power Classes and Maximum Power Consumption

For Power Classes and Maximum Power Consumption see Subclause 7.2.1.

### 4.5.2 Module Power Supply Specification

The following is exceptions and additions to Subclause 5.5.2 of SFF-8679.

Table 5-5 of SFF-8679 no longer applies. In addition the Power\_Override bit and the High Power Class Enable bit do not apply to microQSFP and shall be ignored by the module.

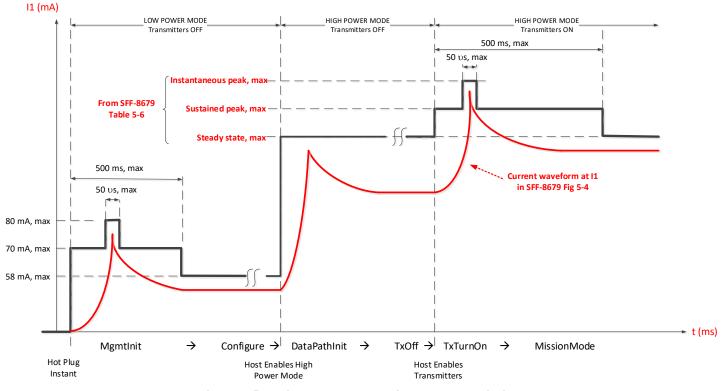

In Figure 5-5 of Subclause 5.5.2 of SFF-8679, inrush current timing is defined. The following Figure 5 is to replace SFF-8679 Figure 5-5.

Figure 5: microQSFP Inrush Current Timing

Table 3 below is an addendum to existing Table 5-6 in SFF-8679, to define Low Power Mode operation. Additionally, the 1.5W entry for Table 5-6 shall refer only to Power Class 1 microQSFP FOUR CHANNEL PLUGGABLE TRANSCEIVER, HOST CONNECTOR, & CAGE ASSEMBLY FORM FACTOR

Page 14

microQSFP Specification Rev 2.5

modules, not Low Power Mode operation. The host power supply voltages including ripple, droop and noise below 100 kHz for VccTxRx and VccMgmt are 3.135 V Minimum, 3.3 V Nominal, and 3.465 V Maximum.

|                                        | 02 110 80 PF |     |     |     |      |

|----------------------------------------|--------------|-----|-----|-----|------|

| Parameter                              | Symbol       | Min | Nom | Max | Unit |

| Power Consumption                      | P_0          | -   | -   | 0.5 | W    |

| Instantaneous peak current at hot plug | Icc_ip_0     | -   | -   | 80  | mA   |

| Sustained peak current at hot plug     | Icc_sp_0     | -   | -   | 70  | mA   |

| Steady state current                   | Icc_0        | -   | Ι   | 58  | mA   |

Table 3: Low Power Mode Operation

### 4.5.3 Host Board Power Supply Noise Output

For Host Board Power Supply Noise Output see Subclause 5.5.3 in SFF-8679

### 4.5.4 Module Power Supply Noise Output

For Module Power Supply Noise Output see Subclause 5.5.4 in SFF-8679

### 4.5.5 Module Power Supply Noise Tolerance

For Module Power Supply Noise Tolerance see Subclause 5.5.5 in SFF-8679

### 4.6 ESD

The following is an exception to the second paragraph of Subclause 5.6 in SFF-8679. All microQSFP Module and host contacts shall withstand 1 000 V electrostatic discharge based on Human Body Model per JEDEC JESD22-A114-B.

### 5. Mechanical and Board Definition

### 5.1 Introduction

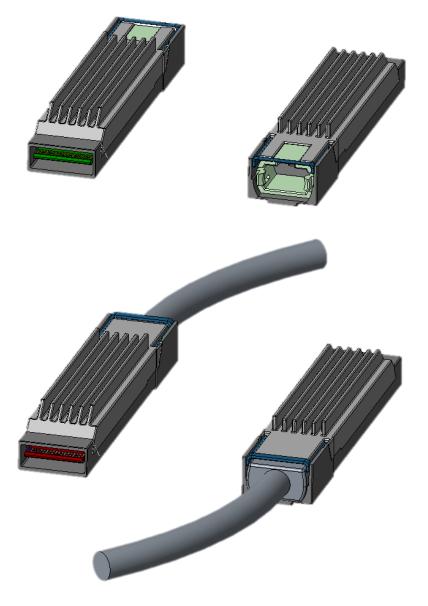

The Module defined in this clause is illustrated in Figure 6. All Pluggable Modules and direct attach cables are designed to mate to the Connector and Cage design defined in this specification. Several Cage to bezel options are allowed. Both metal spring finger and elastomeric EMI solutions are permitted. The microQSFP optical interface shall meet one of the Optical Interfaces defined in Subclause 5.10, and shall mate and unmate with the plug on the optical fiber cabling. Latching mechanism pull tabs are not defined and are not shown.

The overall package dimension shall conform to the indicated dimensions and tolerances indicated in clause 5. The mounting features shall be located such that the products are mechanically interchangeable with the Cage and Connector system. In addition, the overall dimensions and mounting requirements for the Cage and Connector system on a circuit board shall be configured such that the products are mechanically, electrically, and thermally interchangeable and the overall dimensions and insertion requirements for the optical Connector and corresponding fiber optic cable plug shall be such that the products are mechanically and optically interchangeable.

Note: All dimensions are in mm.

Figure 6 - microQSFP Pluggable Module and Direct Attach Cable Rendering

### 5.2 microQSFP Reference Datums and Component Alignment

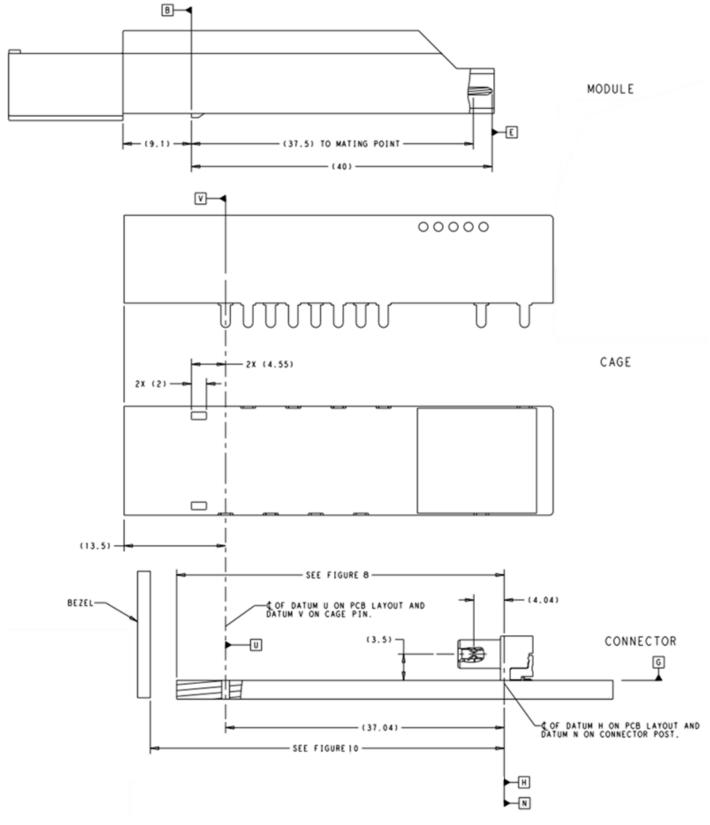

A listing of the reference datums for the various components is contained in Table 4. The alignments of some of the datums are noted. The relationship of the Module, Cage, and Connector relative to the Host Board and Bezel is illustrated in Figure 7 by the location of the key datums of each of the components. In order to reduce the complexity of the drawings, all dimensions are considered centered unless otherwise specified.

| Datum  | Description                                             | Figure Location |

|--------|---------------------------------------------------------|-----------------|

| A      | Bottom surface of Module                                | Figure 6        |

| B      | Latching surface of Module                              | Figure 6        |

| Б<br>С | Width of Module                                         | Figure 6        |

| -      |                                                         |                 |

| D      | Pad surface of Module pc board                          | Figure 7        |

| E      | Front leading surface of Module pc board                | Figure 7        |

| F      | Width of Module pc board                                | Figure 7        |

| G      | Top surface of host pc board                            | Figure 8 & 9    |

| Н      | *Host board thru hole #1 to accept Connector guide post | Figure 8 & 9    |

| J      | Host board thru hole #2 to accept Connector guide post  | Figure 8 & 9    |

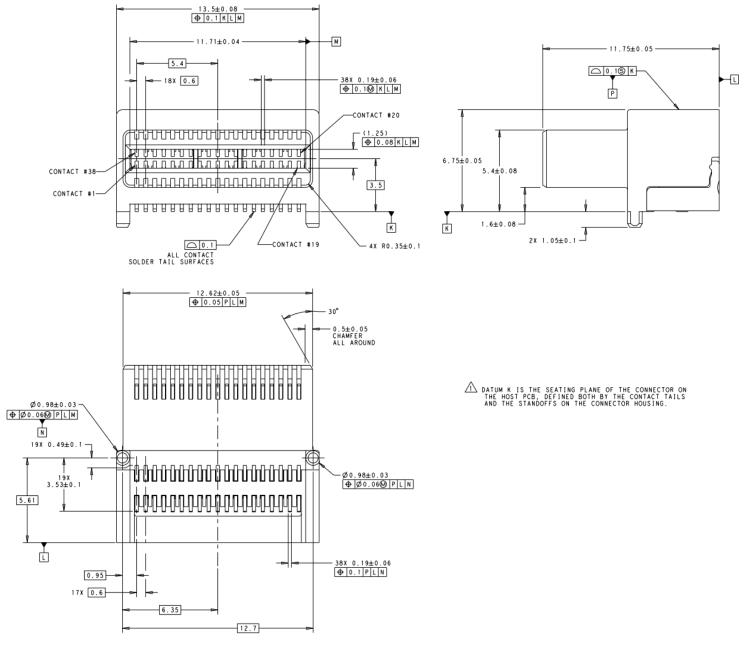

| K      | Seating surface of Electrical Connector                 | Figure 12       |

| L      | Rear surface of Electrical Connector                    | Figure 12       |

| М      | Connector slot width                                    | Figure 12       |

| N      | *Electrical Connector alignment pin                     | Figure 12       |

| Р      | Top Surface of Electrical Connector                     | Figure 12       |

| R      | Seating plane of Cage on host pc board                  | Figure 13       |

| S      | Front surface of Cage                                   | Figure 13       |

| Т      | Width of inside of Cage                                 | Figure 13       |

| U      | **Host board thru hole #1 to accept Cage Pin            | Figure 8        |

| V      | **Cage Pin #1                                           | Figure 13       |

|        |                                                         |                 |

|        | ms H & N are aligned when assembled (see Figure 7)      |                 |

| ** Dat | ums U & V are aligned when assembled (see Figure 7)     |                 |

Table 4 - Definition of Reference Datums

Figure 7 - microQSFP Datum Alignment, Depth

### 5.3 microQSFP Module Mechanical Package Dimensions

A common mechanical outline is used for all microQSFP Modules and direct attach cables. The Module shall provide a means to self-lock with the Cage upon insertion; means to accomplish self-locking is open to vendor implementation, provided it meets the

microQSFP FOUR CHANNEL PLUGGABLE TRANSCEIVER, HOST CONNECTOR, & CAGE ASSEMBLY FORM FACTOR

Page 18

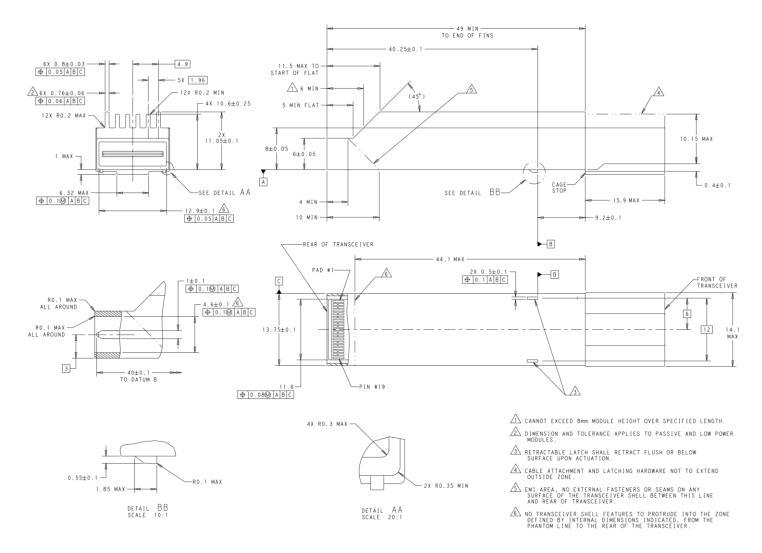

dimensions in Figure 8. The package dimensions for the microQSFP Module are defined in Figure 8 and Figure 9.

Figure 8 - Drawing of microQSFP Module

### 5.3.1 Mating of microQSFP Module PCB to microQSFP Electrical Connector

The microQSFP Module contains a printed circuit board that mates with the microQSFP electrical Connector. The pads are designed for a sequenced mating:

```

First mate - ground contacts

Second mate - power contacts

Third mate - signal contacts

```

The pattern layout for the microQSFP Printed Circuit Board is shown in Figure 9.

Figure 9 - Pattern Layout for microQSFP Printed Circuit Board

### 5.4 Host PCB Layout

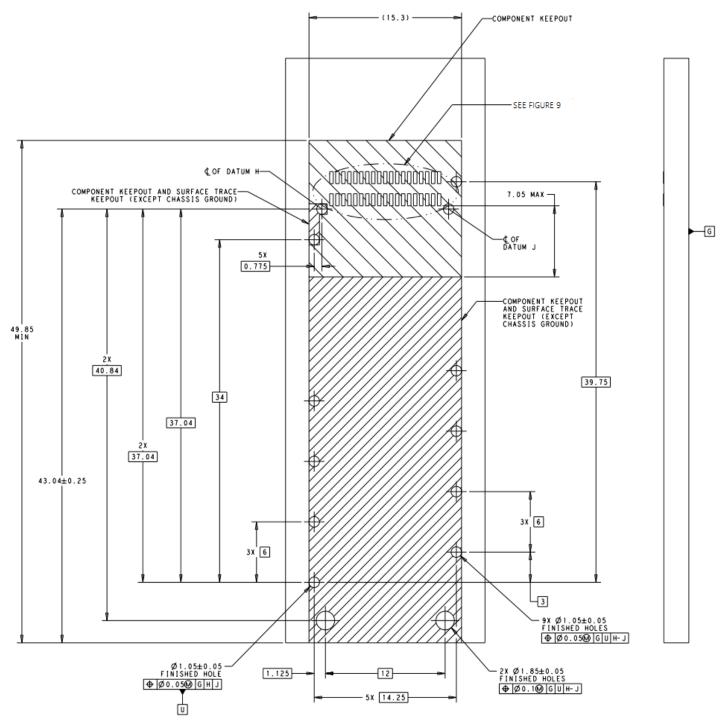

A typical host board mechanical layout for attaching the microQSFP Connector and Cage System is shown in Figure 10 and Figure 11. Location of the pattern on the host board is application specific. See Subclause 5.6 for details on the location of the pattern relative to the bezel.

To achieve 28Gb/s performance pad dimensions and associated tolerances shall be adhered to and attention paid to the host board layout.

Figure 10 - microQSFP Host PCB Mechanical Layout

Figure 11 - microQSFP Host PCB Mechanical Layout

### 5.4.1 Insertion, Extraction and Retention Forces for microQSFP Modules

The requirements for insertion forces, extraction forces and retention forces are specified in Table 5. The microQSFP Cage and Module design combinations shall ensure excessive force applied to a cable does not damage the microQSFP Cage or host Connector. If any part is damaged by excessive force, it should be the cable or media Module and not the Cage or host Connector which is part of the host system. Cable to microQSFP Module retention shall be appropriate to the application, performance can be verified by following industry test methods such as EIA-364-36B or other appropriate specifications.

| Measurement          | Min | Max | Units | Comments                       |  |

|----------------------|-----|-----|-------|--------------------------------|--|

| microQSFP Module     | 0   | 60  | Ν     | Module insertion into host     |  |

| insertion            |     |     |       | Connector & Cage.              |  |

| microQSFP Module     | 0   | 30  | Ν     | Module extraction from host    |  |

| extraction           |     |     |       | Connector & Cage               |  |

| microQSFP Module     | 90  | N/A | Ν     | No damage to Module below 90N  |  |

| retention with latch |     |     |       |                                |  |

| engaged              |     |     |       |                                |  |

| Cage retention in    | 90  | N/A | Ν     | Force to be applied in a       |  |

| Host Board           |     |     |       | direction normal to host board |  |

|                      |     |     |       | top surface, no damage to Cage |  |

| Insertion / removal  | 100 | N/A | Cyc.  | Number of cycles for the       |  |

| cycles, Connector /  |     |     |       | Connector and Cage with        |  |

| Cage                 |     |     |       | multiple Modules.              |  |

| Insertion / removal  | 50  | N/A | Cyc.  | Number of cycles for an        |  |

| cycles, microQSFP    |     |     |       | individual Module.             |  |

| Module               |     |     |       |                                |  |

| Table 5 — | Insertion, | Extraction | and | Retention | Forces |

|-----------|------------|------------|-----|-----------|--------|

|-----------|------------|------------|-----|-----------|--------|

### 5.5 Color Coding and Labeling of microQSFP Modules

Color coding may be defined by vendor specific requirements or by industry agreements. In the absence of such definition, the colors below may be used.

An exposed feature of the microQSFP Module (a feature or surface extending outside of the bezel) are color coded as follows:

microQSFP FOUR CHANNEL PLUGGABLE TRANSCEIVER, HOST CONNECTOR, & CAGE ASSEMBLY FORM FACTOR

Page 22

Beige for 850nm Blue for 1310nm White for 1550nm

Each microQSFP Module shall be clearly labeled. The complete labeling need not be visible when the microQSFP Module is installed and the bottom of the device is the recommended location for the label. Labeling shall include:

Appropriate manufacturing and part number identification Appropriate regulatory compliance labeling A manufacturing traceability code

The label should also include clear specification of the external port characteristics such as:

Optical wavelength Required fiber characteristics Operating data rate Interface standards supported Link length supported

The labeling shall not interfere with the mechanical, thermal or EMI features.

### 5.6 Bezel for Systems using microQSFP Modules

Host enclosures that use microQSFP devices should provide appropriate clearances between the microQSFP Modules to allow insertion and extraction without the use of special tools and a bezel enclosure with sufficient mechanical strength. The microQSFP Module insertion slot should be clear of nearby moldings and covers that might block convenient access to the latching mechanisms, the microQSFP Module, or the cables that plug directly into the Cage.

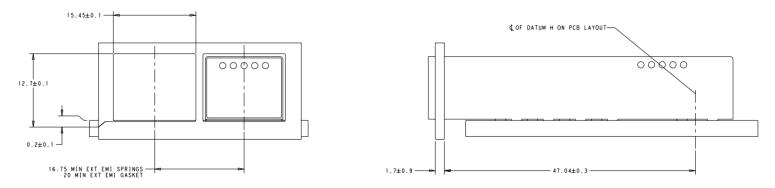

### 5.6.1 Bezel for the Thru Bezel Cage Assembly

The front surface of the Cage assembly passes through the bezel.

Two EMI solutions may be implemented for the thru bezel Cage. If EMI spring fingers are used, they make contact to the inside of the bezel cutouts. If an EMI gasket is used, it makes contact to the inside surface of the bezel. To accept all Cage designs, both bezel surfaces shall be conductive and connected to chassis ground.

The minimum recommended host board thickness for belly to belly mounting of the Connector and Cage assemblies is 2.2 mm.

Figure 12 - Recommended Bezel Design for Cages that extend into or thru Bezel

microQSFP FOUR CHANNEL PLUGGABLE TRANSCEIVER, HOST CONNECTOR, & CAGE ASSEMBLY FORM FACTOR Page 23

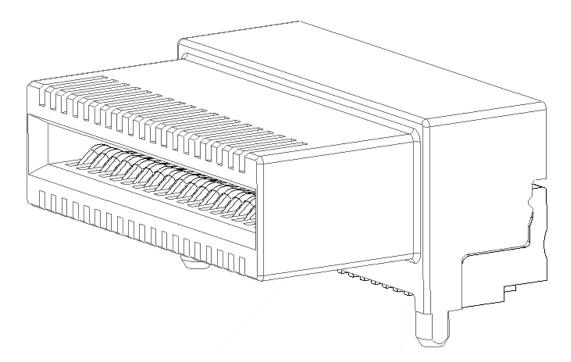

### 5.7 microQSFP Electrical Connector Mechanical

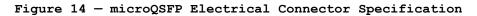

The microQSFP Connector is a 38-contact, right angle surface mount Connector and is shown in Figure 13. The mechanical specifications for the Connector are listed in Table 5 and shown in Figure 14.

Figure 13 - microQSFP Module Electrical Connector Illustration

### 5.8 Individual microQSFP Cage Assembly

For microQSFP a Cage Assembly is utilized that passes through the bezel. The detailed drawings for the Cage assembly options are shown in Figure 15. The purpose of the blocking tab is to prevent damage to the Connector should a Module be inserted in an incorrect orientation.

Figure 15 - 1-by-1 Thru Bezel Cage Design

### 5.9 EMI Cover

In order to prevent contamination of the internal components and to optimize EMI performance, it is recommended that an EMI Cover be inserted into the Cage assembly when no Module is present. The conductivity of the materials should be chosen for the EMI Cover to block EMI emissions. The EMI cover shall be designed such that is can be inserted into a Cage and Connector as defined in this specification.

### 5.10 Optical Interface

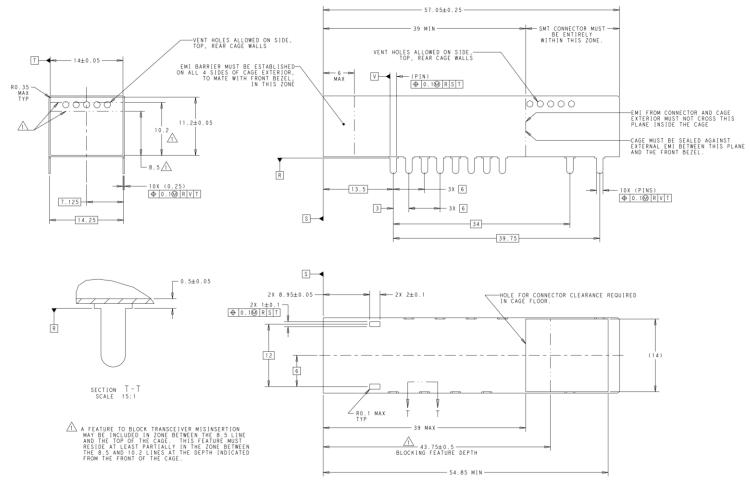

The microQSFP optical interface port shall be either a male MPO connector as specified in IEC 61754-7 (see Figure 16a) or a dual LC as specified in IEC 61754-20 (see Figure 16b).

The four fiber positions on the left as shown in Fig. 14a, with the key slot up, are used for the optical transmit signals (Channel 1 through 4). The fiber positions on the right are used for the optical receive signals (Channel 4 through 1).

The central four fibers may be physically present. Two alignment pins are present.

Figure 16a - microQSFP Optical Receptacle and Channel Orientation for MPO Connector (Viewed from Front of Module)

# Figure 16b - QSFP+ Optical Receptacle and Channel Orientation for dual LC Connector (Viewed from Front of Module)

### 5.11 MPO Optical Cable connection

Aligned key (Type B) MPO patchcords should be used to ensure alignment of the signals between the Modules. The aligned key patchcord is defined in TIA-568 and shown in Figure 16c. The optical Connector is orientated such that the keying feature of the MPO receptacle is on the top.

Figure 16c - microQSFP MPO Optical Patchcord

### 6. Thermal

### 6.1 Thermal Requirements

The microQSFP Module shall operate within one or more of the case temperatures ranges defined in Table 6. The temperature ranges are applicable between 60m below sea level and 1800m above sea level, (Ref. NEBS GR-63) utilizing the host systems designed airflow. Case temperature measurement location shall be vendor specific similar to the current situation with SFP, QSFP, etc. form factors.

| Class      | Case Temperature Range |  |  |  |

|------------|------------------------|--|--|--|

| Standard   | 0 through 70C          |  |  |  |

| Extended   | -5 through 85C         |  |  |  |

| Industrial | -40 through 85C        |  |  |  |

### Table 6 Temperature Range Class of operation

microQSFP is designed to allow for up to 24 adjacent Modules in a single row, ganged, and/or belly-to-belly, with the appropriate thermal design for cooling / airflow (Ref. NEBS GR-63). Airflow around the module and through the Cage is not filtered by design nor is it a requirement of this specification.

### 6.2 Thermal Management Considerations

For microQSFP cooling is typically achieved by allowing front to back airflow to pass through the Module. Ambient air outside the chassis is intended to enter the chassis around the microQSFP Module and through Cage instead of only through other openings in the chassis bezel. This ambient air shall pass around cooling features of the Module, pass into the Cage assembly, and then exit the Cage assembly into the chassis. This design intent allows for increased port density within a chassis rack, while allowing ambient air to not only cool the Module but also allow that air to pass through into the chassis to cool components deeper inside the chassis.

Page 28

microQSFP Specification Rev 2.5 Additionally, the microQSFP Cage should have ventilation holes as allowed in Figure 15. The dimensions of these vent holes are determined by the Cage manufacturers within the bounds set forth in Figure 15. Care should be taken to ensure adequate ventilation through the Cage is attained and that EMI is prevented from penetrating the Cage.

### 7. Management Interface

### 7.1 Introduction

A management interface, as defined in SFF-8636, is specified in order to enable flexible use of the Module by the user.

### 7.2 microQSFP Memory Map

This microQSFP Specification adopts the management interface and memory map requirements found in Clauses 4, 5, and 6 of SFF-8636 except as noted here in Clause 7. This exception list was generated from SFF-8636 rev 2.7. Fields previously used in SFF-8636 Rev 2.7 that are no longer used are now reserved in microQSFP.

| Location                             | Disposition                                                                             | Register Name              | Description                                                                                                                                                                                                                      |

|--------------------------------------|-----------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lower Memory<br>Byte 0 & Byte<br>128 | Identifier<br>value for<br>microQSFP<br>added to SFF-<br>8024 Table 4-1                 | Identifier                 | Additional module type for<br>microQSFP Identifier Value<br>17h.                                                                                                                                                                 |

| Lower Memory<br>Byte 2<br>bits[7:4]  | Changed from<br>Reserved to<br>Current Module<br>state, see<br>Table 9 for<br>encoding. | Module_State               | Current module state,<br>encoded (see Table 9 for<br>encoding.)                                                                                                                                                                  |

| Lower Memory<br>Byte 2 bit 0         | Change from<br>Data_Not_Ready<br>flag to<br>Reserved                                    | Data_Not_Ready flag        | Functionality replaced by<br>State_changed flag, this<br>register bit is reserved<br>for future use.                                                                                                                             |

| Lower Memory<br>Byte 6 bit 0         | Change from<br>Initialization<br>Complete flag<br>to<br>State_changed<br>flag           | State_changed flag         | Flag to indicate state<br>transition from a<br>transient state to a<br>parked state. Setting this<br>flag shall result in the<br>module asserting IntL.<br>This flag shall be cleared<br>upon read.                              |

| Lower Memory<br>Byte 93 bit 0        | Change from<br>Power override<br>to Reserved                                            | Power override             | microQSFP does not have a<br>dedicated LPMODE contact,<br>this register bit is<br>reserved for future use                                                                                                                        |

| Lower Memory<br>Byte 93 bit 1        | Change Power<br>Set<br>Description                                                      | Power_Set                  | Power set to Low Power<br>Mode Default 1                                                                                                                                                                                         |

| Lower Memory<br>Byte 93 bit 2        | Change from<br>High Power<br>Class Enable<br>to Reserved                                | High Power Class<br>Enable | This bit is no longer<br>needed, because the host<br>can read all power classes<br>and determine support, so<br>clearing the Power set bit<br>will enable power classes<br>1-7. This register bit is<br>reserved for future use. |

### Table 7 microQSFP Exceptions to SFF-8636 Memory Map Definition

microQSFP Specification Rev 2.5

| Lower Memory   | Changed from   | M-Module State      | Masking Bit for Module     |

|----------------|----------------|---------------------|----------------------------|

| Byte 103 bit 0 | Reserved to M- | Change              | State Change Flag.         |

| Byce 105 Dit 0 |                | Change              | State change riag.         |

|                | Module State   |                     |                            |

|                | Change         |                     |                            |

| Lower Memory   | Change power   | Extended Identifier | microQSFP needs additional |

| Byte 129 bits  | classes for    | Values              | power classes not          |

| [7:5]          | bits [7:6],    |                     | designated in SFF-8636.    |

|                | change bit 5   |                     | See Table 8 for encodings. |

|                | from Reserved  |                     |                            |

|                | to power class |                     |                            |

|                | use.           |                     |                            |

| Lower Memory   | Change from    | Extended Identifier | These bits are no longer   |

| Byte 129 bits  | Unused and     | Values              | needed to define power     |

| [1:0]          | Power Classes  |                     | classes, all power classes |

|                | to Reserved.   |                     | are defined in bits [7:5]. |

|                |                |                     | See Table 8 for encodings. |

| Lower Memory   | Changed from   | Max DataPathInit Du | Max duration of            |

| Byte 114 bits  | Reserved to    | ration –            | DataPathInit state. See    |

| [3:0]          | Max DataPathIn |                     | Table 10 for encodings.    |

| [0.0]          | it Duration    |                     | Table it for encourige.    |

| Lower Memory   | Changed from   | Max TX TurnOn Durat | Max duration of TX TurnOn  |

| Byte 114 bits  | Reserved to    | ion                 | state. See Table 10 for    |

| [7:4]          | Max TX TurnOn  | 1011                | encodings.                 |

| [/•4]          |                |                     | encourngs.                 |

|                | Duration       |                     |                            |

The reader should also note that microQSFP adds a VccMgmt supply that does not exist in SFF-8636. Therefore, all references to Vcc in SFF-8636 are applicable to the VccTxRx rail and not the VccMgmt rail.

### 7.2.1 Extended Identifier

The extended identifier provides additional information about the free side device. For example, the identifier indicates if the free side device contains a CDR function and identifies the power consumption class it belongs to.

The power class identifiers specify maximum power consumption over operating conditions and lifetime with all supported settings set to worst case values.

| Table 0            | Excended identifier values (nower memory by |

|--------------------|---------------------------------------------|

| Bit                | Device Type                                 |

| 7,6,5              | 000: Power Class 1 (0.5 W max.)             |

|                    | 001: Power Class 2 (1.5 W max.)             |

|                    | 010: Power Class 3 (2.5 W max.)             |

|                    | 011: Power Class 4 (3.5 W max.)             |

|                    | 100: Power Class 5 (5.0 W max.)             |

|                    | 101: Power Class 6 (7.0 W max.)             |

|                    | 110: Power Class 7 (9.0 W max.)             |

|                    | 111: Power Class 8 (>9.0 W) *               |

| 4                  | 0: No CLEI code present in Page 02h         |

|                    | 1: CLEI code present in Page 02h            |

| 3                  | 0: No CDR in TX                             |

|                    | 1: CDR Present in TX                        |

| 2                  | 0: No CDR in RX                             |

|                    | 1: CDR Present in RX                        |

| 1-0                | Reserved                                    |

| * See vendor docum | entation for specific power requirements.   |

Table 8 Extended Identifier Values (Lower Memory Byte 129 bits 7:0)

## 7.2.2 Module\_State Register Encodings

microQSFP FOUR CHANNEL PLUGGABLE TRANSCEIVER, HOST CONNECTOR, & CAGE ASSEMBLY FORM FACTOR Page 30

Encodings for the Module\_State register are shown in Table 9. Passive copper cables implemented with static EEPROMs shall utilize encoding 0000b.

| Encoding Bit<br>order (7,6,5,4) | State                                 |

|---------------------------------|---------------------------------------|

| 0000b                           | Module does not support state machine |

| 0001b                           | MgmtInit                              |

| 0010b                           | Configure                             |

| 0011b                           | DataPathInit                          |

| 0100b                           | TX_Off                                |

| 0101b                           | TX_TurnOn                             |

| 0110b                           | MissionMode                           |

| 0111b                           | RevertLowPwr                          |

| 1000b-1111b                     | Reserved                              |

### Table 9 Module\_State Encodings (Lower Memory Byte 2 bits 7:4)

### 7.2.3 Transient State Duration Encodings

The Max\_DataPathInit\_Duration (Lower Memory Byte 114 bits 3:0) and Max\_TX\_TurnOn\_Duration (Lower Memory Byte 114 bits 7:4) registers are used to allow the module to inform the host of the maximum duration of transient states. Note that the module may interrupt the host at any time before the maximum duration reported, to report that the state is complete. Table 10 defines the encodings used for both registers.

### Table 10 Transient State Duration Encodings (Lower Memory Byte 114 bits 7:4 & bits 3:0)

| Encoding Bit order    | Maximum State Duration                                      |

|-----------------------|-------------------------------------------------------------|

| (7,6,5,4) & (3,2,1,0) |                                                             |

| d0000b                | Maximum state duration is less than 1 ms. This state is not |

|                       | reported in the Module_State register, and no interrupt is  |

|                       | generated upon entry into next parked state                 |

| 0001b                 | 1 ms <= maximum state duration < 5 ms                       |

| 0010b                 | 5 ms <= maximum state duration < 10 ms                      |

| 0011b                 | 10 ms <= maximum state duration < 50 ms                     |

| 0100b                 | 50 ms <= maximum state duration < 100 ms                    |

| 0101b                 | 100 ms <= maximum state duration < 500 ms                   |

| 0110b                 | 500 ms <= maximum state duration < 1 s                      |

| 0111b                 | 1 s <= maximum state duration < 5 s                         |

| 1000b                 | 5 s <= maximum state duration < 10 s                        |

| 1001b                 | 10 s <= maximum state duration < 1 min                      |

| 1010b                 | 1 min <= maximum state duration < 5 min                     |

| 1011b                 | 5 min <= maximum state duration < 10 min                    |

| 1100b                 | 10 min <= maximum state duration < 50 min                   |

| 1101b                 | Maximum state duration >= 50 min                            |

| 1110b                 | Reserved                                                    |

| 1111b                 | Reserved                                                    |

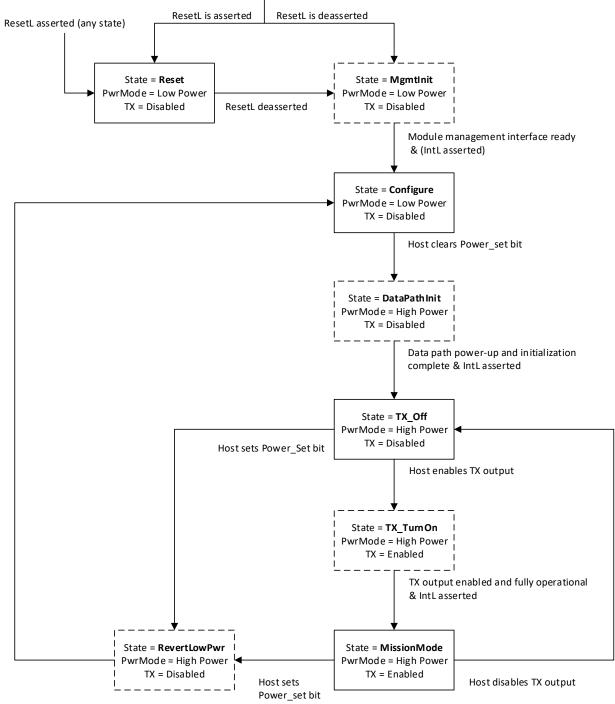

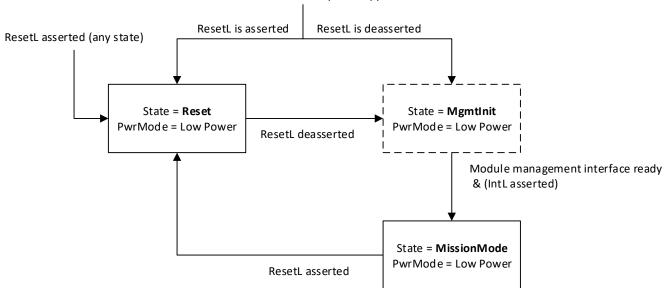

### 7.3 microQSFP State Machine

The module behaviors and available interfaces to the host are defined using the state machines shown in Figure 17 and Figure 18 below. The Figure 17 state machine is applicable to modules that contain active electronics in the high-speed data path. The Figure 18 state machine is applicable to passive copper cable assemblies.

States with dashed boxes are transient states with a variable duration, depending on the module implementation. The module reports the maximum duration of the DataPathInit and TX\_TurnOn states in the Max\_DataPathInit\_Duration and Max\_TX\_TurnOn\_Duration registers in the memory map. In general, host interactions with the module should be minimized during these transient states, with memory map accesses limited to read-only static register content. Dynamic register content is unreliable during transient states.

microQSFP FOUR CHANNEL PLUGGABLE TRANSCEIVER, HOST CONNECTOR, & CAGE ASSEMBLY FORM FACTOR

### microQSFP Specification Rev 2.5

States with solid boxes are parked states, which require host interaction. The duration of these states is completely controlled by the host, with exit from the state only occurring after the module receives the applicable trigger from the host. The trigger for each state is defined in the state diagrams and detailed descriptions below.

The memory map contains a Module\_State register to report the current state of the module. Some transient states may be so short that the Module\_State register is not updated. Refer to Subclause 7.2.2 for the definition of the Module\_State register encodings and Subclause 7.2.3 for transient state duration encodings.

All modules shall power up in Low Power Mode upon insertion or assertion or deassertion of ResetL. When active modules are in low power mode, the module receiver high speed signal outputs shall be quiescent and the transmitter optical outputs shall be disabled. All passive copper cable assemblies shall be fully functional immediately upon insertion.

When the host software has configured the active module and is ready to activate the high-speed data path, the host software shall put the module into High Power Mode, using the control bits in Lower Memory Page Byte 93 control bits 0 and 1.

In Table 5-4 of Subclause 5.5.2 of SFF-8679, the default value for the Power\_Set bit is 1. Both bits 1 and 0 shall be set to move the module to High Power Mode.

The host shall apply power to both the VccMgmt and VccTxRx rails upon module insertion.

Module insertion & power applied

Figure 17 - microQSFP Active Module State Machine

### Module insertion & power applied

Figure 18 - microQSFP Passive Copper Cable State Machine

### 7.3.1 MgmtInit State (Transient)

The MgmtInit state is a transient state that is entered any time the module is brought out of Reset, due to deassertion of the ResetL signal or upon initial insertion and application of power to the VccMgmt and VccTxRx contacts. For implementations supporting only passive copper cables, the host may or may not apply VccTxRx. The MgmtInit state is applicable to both active modules and passive copper cable assemblies.

During this state, the module shall initialize the management interface and configure the memory map for access by the host. The module may perform limited power-up of the high-speed data path circuitry, however the module shall remain in Low Power mode throughout this state. The module may ignore all 2-wire serial interface transactions while in this state.

The module shall not assert IntL during MgmtInit. If catastrophic faults occur, the module shall transition immediately to the Configure state to report the fault. The module shall report all non-catastrophic faults and warnings that are valid after transitioning to the Configure state.

Before the module exits this state, all memory map register locations shall be set to their power-on defaults. The module shall have completed MgmtInit in accordance with Mgmtinit\_Duration as defined in Table 12. The duration of the MgmtInit state, MgmtInit\_Duration, is the time from power on (defined as the instant when supply voltages reach and remain at or above the minimum level specified in SFF-8679 Table 5-6), hot plug or rising edge of reset until the module has configured the memory map to default conditions and activated the management interface.

### 7.3.2 Configure State (Parked)

The Configure state is a parked state only applicable to active microQSFP modules. During this state, the host may configure the module using the management interface and memory map. Some example configuration activities include reading the ID and device property fields, setting CDR and other channel attributes and configuration of monitor masks. Details of host-module interactions in the Configure State are implementation dependent and are outside the scope of this specification.

Upon entry into the Configure state, the module shall set the Module\_State register to the Configure state, set the State\_Changed flag and any applicable fault and warning flags that are valid after transitioning to the Configure state, and assert the IntL

microQSFP FOUR CHANNEL PLUGGABLE TRANSCEIVER, HOST CONNECTOR, & CAGE ASSEMBLY FORM FACTOR

microQSFP Specification Rev 2.5

signal. The host shall read the State\_Changed flag along with all other fault and warning flags to deassert the IntL signal.

Throughout the Configure state, the module shall remain in Low Power Mode and the TX output shall be disabled. The module shall ignore host requests to enable the module TX while in this state.

Prior to exit from this state, the host shall enable all applicable host transmitters and provide compliant signals, so that the module can configure TX electrical input circuitry while in the DataPathInit state.

When the host has completed module configuration, the host may enable full power up of the module by writing a 0 in the Power\_Set bit (Lower Memory Page Byte 93 bit 1) in the memory map.

### 7.3.3 DataPathInit State (Transient)

The DataPathInit state is a transient state where the module powers up the TX and RX high speed data path electronics and applies module configuration settings defined in the module memory map. This state is applicable only to active modules. Example activities during this state include adaptation of module CTLE, TX CDR lock, and RX equalization enable, etc. The duration of the DataPathInit state, DataPathInit\_Duration, is the time from the falling clock edge after the Stop bit of the Power\_Set bit write transaction to the assertion of the initialization completed IntL (IntL Vout = Vol), both times are observed at the module. The maximum duration of the DataPathInit state shall be identified by the module vendor in the Max\_DataPathInit\_Duration register, Lower Memory Byte 114 bits [3:0]. Encodings for Max DataPathInit Duration are defined in Table 10.

Upon entry into the DataPathInit state, the module shall enter High Power mode and set the Module State register to the DataPathInit state.

Throughout the DataPathInit state, the TX output shall be disabled. The module shall ignore host requests to enable the module TX while in this state. The host shall minimize 2-wire serial transactions while in this state. Dynamic memory map content may be unreliable while in this state and should not be read or written.

The module shall not assert IntL during DataPathInit. If catastrophic faults occur, the module shall transition immediately to the TX\_Off state to report the fault. The module shall report all non-catastrophic faults and warnings that are valid after transitioning to the Tx Off state.

When the module has completed power-up and initialization of the TX and RX high-speed data path circuitry, the module shall transition to the TX Off state.

### 7.3.4 TX Off State (Parked)

The TX\_Off state is a holding state where the module TX and RX electronics has been fully powered and configured but is waiting for the host to enable the module TX output. This state is only applicable to active modules.

Upon entry into the TX\_Off state, the module shall set the Module\_State register to the TX\_Off state, set the State\_Changed flag and any valid fault and warning flags, and assert the IntL signal. The host shall read the State\_Changed flag along with all other fault and warning flags to deassert the IntL signal.

Throughout the TX\_Off state, the module shall remain in High Power Mode and the TX output shall be disabled.

A Host enables the transition to the TX\_TurnOn state TX by writing a 0 in each and every TX Disable bit (Lower Memory Byte 86 bits 3:0).

### 7.3.5 TX TurnOn State (Transient)

microQSFP FOUR CHANNEL PLUGGABLE TRANSCEIVER, HOST CONNECTOR, & CAGE ASSEMBLY FORM FACTOR

### microQSFP Specification Rev 2.5

The TX\_TurnOn state is a transient state where the module enables its TX output. This state is applicable only to active modules. The duration of the TX\_TurnOn state, TX\_TurnOn\_Duration, is the time from the falling clock edge after the Stop bit of the last TX Disable bit write transaction to until the optical output rises above 90% of nominal, both times are observed at the module. The maximum duration of the TX\_TurnOn state shall be identified by the module vendor in the Max\_TX\_TurnOn\_Duration register, Lower Memory Byte 114 bits [7:4]. Encodings for Max\_TX\_TurnOn\_Duration are defined in Table 10.